Katie Bradford, Ho-Jung Yang, Alex Hatzis, Anthony Viego

## Introduction

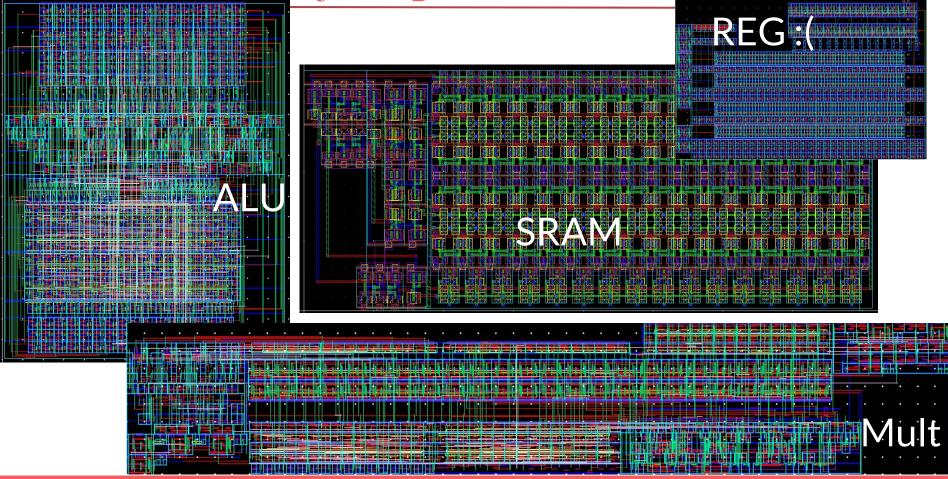

# 16 bit processor

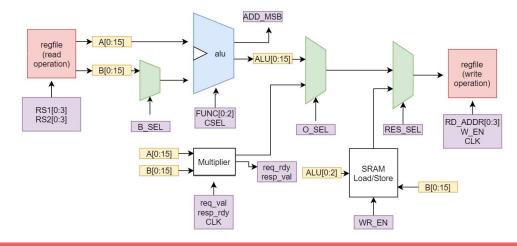

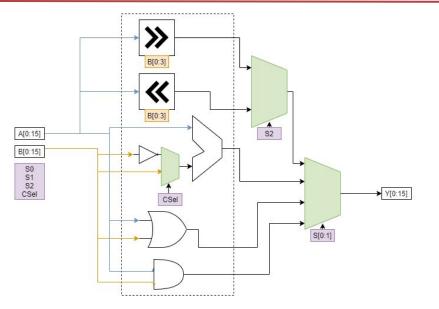

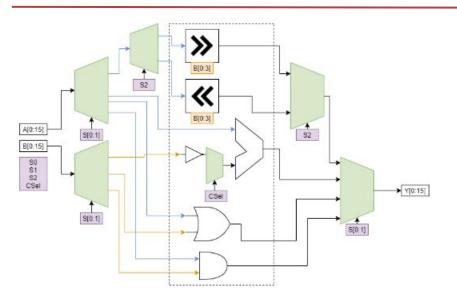

- ALU

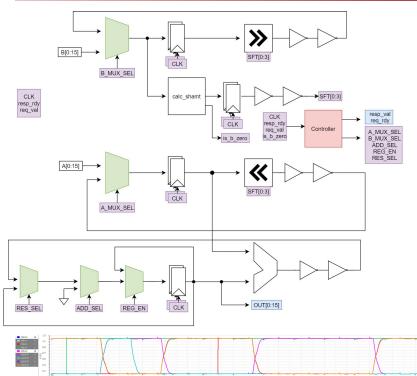

- Multiplier

- Read/Write SRAM Memory

- Register File

- Full System Architecture & Applications

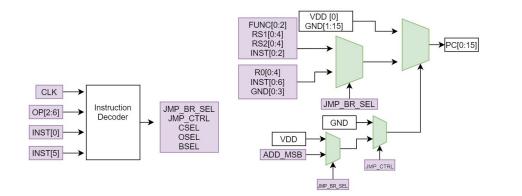

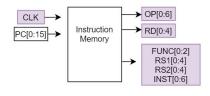

#### **System Architecture**

Instruction memory in verilog Decoder in hardware (not laid out)

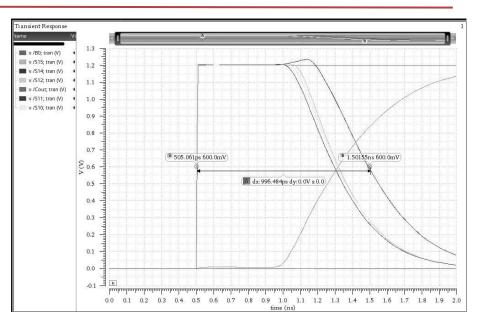

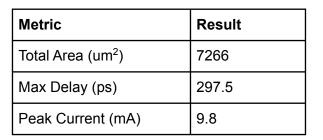

## **ALU Performance**

| Metric                        | Result |

|-------------------------------|--------|

| Total Area (um <sup>2</sup> ) | 4354   |

| Max Delay (ps)                | 996    |

| Max Current (mA)              | 10     |

- Add was the longest delay, worst case from lab

- Brent-Kung adder

## **ALU Comparison**

| Metric                        | Base   | Muxed Input |

|-------------------------------|--------|-------------|

| Total Area (um <sup>2</sup> ) | 4354   | 5919        |

| Max Delay (ps)                | 996    | 1030        |

| Power Consumed<br>(mW)        | .053mW | .27mW       |

Goal: improve power by reducing dynamic power switching

Current was higher overall due to DC, would have been better to power gate

Delay not too much higher due to lower fanout

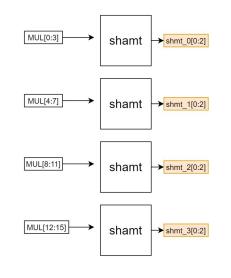

## **Multiplier Performance**

340 15.0

- Transport - Control - Co

/DET-0>

| Metric                        | Result |

|-------------------------------|--------|

| Total Area (um <sup>2</sup> ) | 10,984 |

| Max Delay (ps)                | 1333   |

| Peak Current (mA)             | 10.78  |

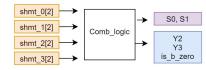

## **Read/Write Memory Performance**

| Metric                        | Result         |

|-------------------------------|----------------|

| Total Area (um <sup>2</sup> ) | 700.2          |

| Max Delay, Reading<br>(ps)    | 25 **(loosely) |

| Peak Current (mA)             | 3.78           |

- Four 16-bit entries

- SRAM

- Ratio'd logic

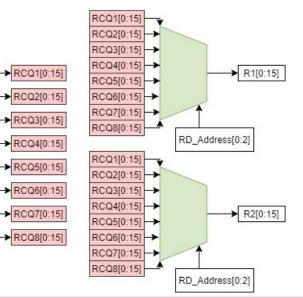

## **Reg File Performance**

• Sub blocks laid out, not full layout

RD Address[0:8]

Buffer

- WE and RD address AND to enable writing DFFs

- Can read two regs and write in same cycle

WE

Bitwise And

► D[0:15]

CLK

WE[0:8]

DFF

DFF

DFF

DFF

DFF

DFF

DFF

DFF

Reg Cell 1

Reg Cell 2

Reg Cell 3

Reg Cell 4

Reg Cell 5

Reg Cell 6

Reg Cell 7

Reg Cell 8

D[0:15]

D[0:15]>

D[0:15]

D[0:15]

D[0:15]>

D[0:15]

D[0:15]

D[0:15]

• 8 total registers

Decoder

Data\_In[0:8]

DFF

RD Address[0:2]

CLK

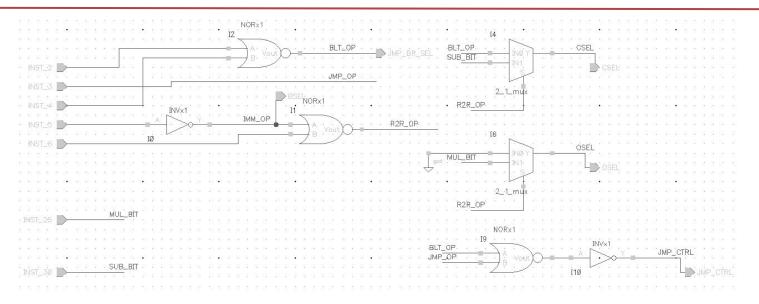

#### **ISA/Test Bench**

ISA from Comp Arch, 32 bit instructions mapped to 16 bit operations

Instructions stored as machine code inside a Verilog block (Instruction ROM) PC Register and PC adder both internal to instruction memory to reduce repeated blocks

Decode verilog instructions to control signals using dedicated hardware

## Full System Performance (\*\*Not fully laid out)

#### **Operations Tested:**

- Multiplying 3\*4, R2R

- Add, subtract, OR, AND, shift

- Memory instructions

- Store and Load

- Fibonacci

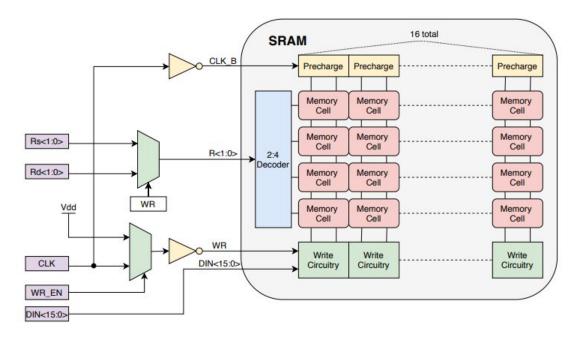

| Metric                             | Result                 |

|------------------------------------|------------------------|

| Total Area                         | 23,304 um <sup>2</sup> |

| Max Theoretical Clock<br>Frequency | 600 MHz                |

| Max Clock Frequency                | 200MHz                 |

| Max Current                        | 10.78 mA               |

Real max frequency closer to 200MHz - adder was built with low drive strength (10fF), much higher when inputting to reg file

## **Full System Application**

#### Finding the next two Fibonacci numbers in a sequence

| INST # | OP   | RS1 | RS2/Imm | Rd |

|--------|------|-----|---------|----|

| 0      | ANDI | RO  | 0       | RO |

| 1      | ORI  | RO  | 8       | R1 |

| 2      | ORI  | RO  | 13      | R2 |

| 3      | ORI  | RO  | 2       | R7 |

| 4      | ADD  | R1  | R2      | R3 |

| 5      | OR   | RO  | R2      | R1 |

| 6      | OR   | RO  | R3      | R2 |

| 7      | ADDI | R7  | -1      | R7 |

| 8      | BLT  | RO  | R7      | -4 |

|    | R0    | R1    | R2    | R3    | R4    | R5    | R6    | R7    |

|----|-------|-------|-------|-------|-------|-------|-------|-------|

| 1  | 32767 | 32767 | 32767 | 32767 | 32767 | 32767 | 32767 | 32767 |

| 2  | 0     | 32767 | 32767 | 32767 | 32767 | 32767 | 32767 | 32767 |

| 3  | 0     | 8     | 32767 | 32767 | 32767 | 32767 | 32767 | 32767 |

| 4  | 0     | 8     | 13    | 32767 | 32767 | 32767 | 32767 | 32767 |

| 5  | 0     | 8     | 13    | 32767 | 32767 | 32767 | 32767 | ,2    |

| 6  | 0     | 8     | 13    | _ 21  | 32767 | 32767 | 32767 | 2     |

| 7  | 0     | 13    | 13    | 21    | 32767 | 32767 | 32767 | 2     |

| 8  | 0     | 13    | 21    | 21    | 32767 | 32767 | 32767 | 2     |

| 9  | 0     | 13    | 21    | 21    | 32767 | 32767 | 32767 | 1     |

| 10 | 0     | 13    | 21    | 21    | 32767 | 32767 | 32767 | 1     |

| 11 | 0     | 13    | 21    | 34    | 32767 | 32767 | 32767 | 1     |

| 12 | 0     | 21    | 21    | 34    | 32767 | 32767 | 32767 | 1     |

| 13 | 0     | 21    | 34    | 34    | 32767 | 32767 | 32767 | 1     |

| 14 | 0     | 21    | 34    | 34    | 32767 | 32767 | 32767 | 0     |

## **Team Member Contributions**

~Generally~

Katie - ALU

Alex - Top level design and testing, reg file

HJ - Read/write Memory

Anthony - Multiplier

#### Appendix A: layout pix